# Design and Implementation of Low Power and High Speed Shift Register Using Fin FET

R.Gurumurugan<sup>1</sup>, V.Senthamizh Selvan<sup>2</sup>, S.Viswaganth<sup>3</sup>

\*(Electronics and Communication Engineering, University College of Engineering Ariyalur, India) gurumurugan968@gmail.com and senthamizhselvan111@gmail.com

**Abstract:** The electrostatic benefit of using a silicon-on-insulator wafer substrate versus a bulk-silicon wafer substrate with optimized supersteep retrograde doping for a low-power 7-/8-nm.SOI FinFET technology is projected to provide only slight improvement in performance and minimum cell operating voltage as compared with SSR FinFET technology. In this work we are applying valuable power gating schemes to FinFET based shift register to enhance its performance by reducing the leakage current in standby mode. This provides the motivation to explore the design of low leakage FinFET based Shift register with power reduction techniques. **Keywords:** SOI FinFET, Low Power, D Flip-Flop, SVL Techniques, Types of Shift Register.

## I. Introduction

BULK-SILICON (Si) trigate transistors have been adopted by the industry since the22-nm CMOS technology node to facilitate further component miniaturation. The use of a silicon-on-insulator (SOI) substrate eliminates sub-fin leakage current in FinFETs without the need for "punch through stopper" (PTS) doping at the base of the gated fin region, and hence provides for improved transistor performance as well as reduced variation arising from random dopant fluctuations (RDFs). Even for the idle circuit Metal Oxide Semiconductor (MOS) devices will not able to properly turn-off, as a result of which "off-state current" will flow through the circuit. The major sources for this off-state current: (1) Sub-threshold leakage, (2) Gate leakage current and (3) Band-to- Band tunneling leakage current. In this paper, we propose three circuit techniques to control the off-state current, using different PULL-UP and PULLDOWN networks of NMOS and PMOS are applied to FinFET based Shift register one after another. Due to this treatment of PULL-UP and PULLDOWN network controlled voltage supply is obtained and the current driving capability of the design is increased, hence less Gate leakage current is formed.

II. Device Simulation And Design Optimization

Fig.1.1 Shematic of FinFET Fig.1.2 schematic of SVL technique

#### A.FINFET

FinFET technology takes its name from the fact that the FET structure used looks like a set of fins when viewed. The main characteristic of the FinFET is that it has a conducting channel wrapped by a thin silicon "fin" from which it gains its name. The thickness of the fin determines the effective channel length of the device. In terms of its structure, it typically has a vertical fin on a substrate which runs between a larger drain and source area. This protrudes vertically above the substrate as a fin. The gate orientation is at right angles to the vertical fin. And to traverse from one side of the fin to the other it wraps over the fin, enabling it to interface with three side of the fin or channel. This form of gate structure provides improved electrical control over the channel conduction and it helps reduce leakage current levels and overcomes some other short-channel effects.

## **B. SVL TECHNIQUES**

Leakage current flowing through OFF transistors is reduced in above circuit by applying SVL technique as shown in Fig. Leakage current flowing through OFF transistors is reduced in above circuit by applying SVL technique as shown in Fig. 4 This technique is implemented in the upper side as PULL UP network connected to the supply Vdd and lower side as PULL DOWN network connected with ground of 5T DFF. The PULL UP network contain one PMOS (Psw1) switch which is connected in parallel with a NMOS (Nsw1) switch such that during active mode as Clk is high which causes Psw1 switch to turn ON hence connecting the basic 5T D flip flop to Vdd supply voltage while during the standby mode of operation Clk is low turning ON the Nsw1 switch which provides virtual supply to 5T DFF. In the lower side SVL one PMOS switch is again in parallel connection with one NMOS switch so in active mode NMOS switch (Nsw2) turns ON connecting ground to 5T DFF while in standby mode PMOS switch Psw2 turn ON and provide virtual ground to 5T DFF for normal circuit operation but during the standby mode for controlling the leakage current through OFF transistors the Nsw1 and Psw2 switches provides virtual supply and virtual ground which reduces the sub leakage current in OFF transistors.

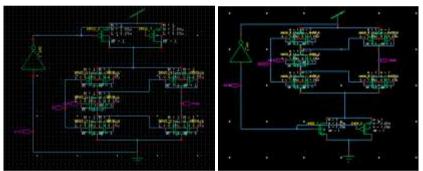

#### **B.1.UPPER SVL TECHNIQUE:**

In U-SVL technique, a combination of one PMOS & two NMOS are connected in parallel. So that an input clock pulse is applied at the PMOS of circuit of U-SVL and rest of all NMOS are connected to drain terminal. Shift register using U-SVL scheme is depicted in Figure below. Under this scheme, full supply voltage of Vddisapplied to the semiconductor device. The U-SVL schematic is intended on a broad channel pull up pMOSFET& pull down n-MOSFET. The circuit diagram of shift register designed using U-SVL technique. This approach is more valuable for reducing the power consumption also for the leakage current. For very low Power consumption, U-SVL technique is most responsible. Shift register designed at micron CMOS technology, produces the better results. But now a day of nanotechnology at Vdd = 0.7 V, power consumption.

Fig 1.3 Upper SVL techniqueFig.1.4Lower SVL technique

#### **B.2. LOWER SVL TECHNIQUE**

In L-SVL technique a combination of one NMOS & two PMOS are connected in parallel. So that an input clock pulse is applied at the NMOS of circuit of L-SVL and rest of all PMOS are connected to ground. This ground terminal is connected to the LSVL circuit. Shift register using L-SVL scheme is shown in Figure 3. The switch brings 0Volt at the ground node & raises the ground level (virtual ground). The L-SVL circuits initiates wide channels pull down n-MOSFET and pull up p-MOSFET.Depending upon the clock and inputs, variation in output is varied. Figure 3 shows the variation of power Vs supply voltage of shift register design using L-SVL scheme. Where the power consumption is measured at the various supply voltage at Vdd = 0.7 V, power consumption is  $1.24\mu$ w.

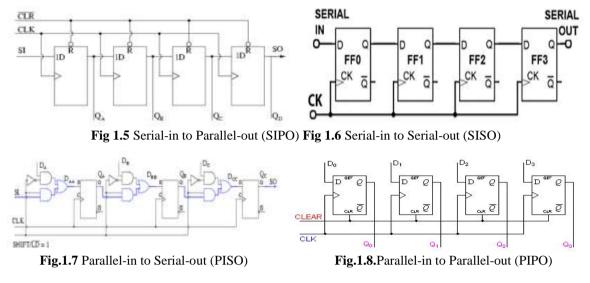

#### C. SHIFT REGISTER

A shift register is a cascade of flip flops, sharing the same clock, in which the output of each flip-flop is connected to the 'data' input of the next flip-flop in the chain, resulting in a circuit that shifts by one position the 'bit array' stored in it, 'shifting in' the data present at its input and 'shifting out' the last bit in the array, at each transition of the clock input. More generally, a shift register may be multidimensional, such that its 'data in' and stage outputs are themselves bit arrays: this is implemented simply by running several shift registers of the same bit-length in parallel.

Shift registers can have both parallel and serial inputs and outputs. These are often configured as 'serial-in, parallel-out' (SIPO) or as 'parallel-in, serial-out' (PISO). There are also types that have both serial and

parallel input and types with serial and parallel output. There are also 'bidirectional' shift registers which allow shifting in both directions:  $L \rightarrow R$  or  $R \rightarrow L$ .

#### TYPES OF SHIFT REGISTER

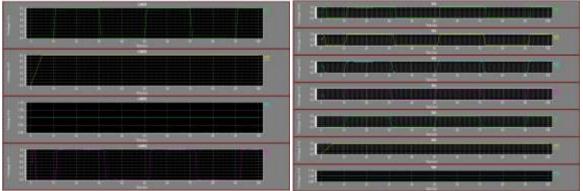

**D. SIMULATED OUTPUT**

- Serial-in to Parallel-out (SIPO) -The register is loaded with serial data, one bit at a time, with the stored data being available at the output in parallel.

- Serial-in to Serial-out (SISO) The data is shifted serially "IN" and "OUT" of the register, one bit at a time in either a left or right direction under clock control.

- Parallel-in to Serial-out (PISO) The parallel data is loaded into the register simultaneously and is shifted out of the register serially one bit at a time under clock control.

- Parallel-in to Parallel-out (PIPO) the parallel data is loaded simultaneously into the register, and transferred together to their respective outputs by the same clock pulse.

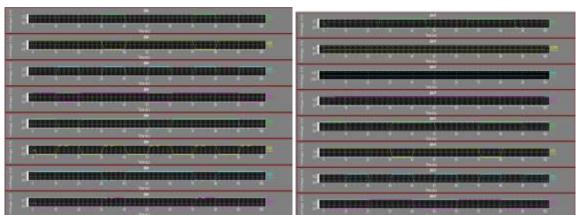

Fig 1.9 Serial in serial out(SISO) Fig 1.10 Serial in parallel out(SIPO)

Fig 1.11 Parallel in parallel out(PIPO) Fig 1.12 Parallel in serial out(PISO)

## **III. Results**

Table.1.1 Comparison of CMOS shiftTable 1.2 Comparison of shift register register and FinFET shift registerwith and without SVL

| Parameters  | CMOS shift<br>register | FinFET shift<br>Register | Parameter         | Shift register with | Shift register<br>without SVL |

|-------------|------------------------|--------------------------|-------------------|---------------------|-------------------------------|

| Power       | 4.954777e-007          | 1.090036e-006 watts      | Turunceer         | SVL technique       | technique                     |

| consumption | watts                  |                          | Power consumption | 1.007419e-006 watts | 1.090036e-006 watts           |

| Delay       |                        |                          |                   |                     |                               |

| measurement | -3.4599e-008           | -3.8195e-008             | Delay measurement | -3.8195e-008        | -3.8579e-008                  |

Table.1.4 Comparison of types of shift register using FinFET and SVL technique.

| PARAMETER | SISO       | SIPO       | PIPO       | PISO       |

|-----------|------------|------------|------------|------------|

| Power     | 1.007419e- | 1.039051e- | 1.183502e- | 1.666446e- |

|           | 006 watts  | 006 watts  | 006 watts  | 006 watts  |

## **IV.** Conclusion

CMOS and SOI FinFET with SVL technologies are projected to provide substantial reductions in power and increase in speed for minimum 5T-shift register. The proposed circuit is a low power consumption design forSVL based shift register with power reduction of 83mW. The delay is reduced by FinFet technology by 38ns. The design overcomes short channel effects as the calculated leakage current is very small in comparison with the leakage which occur in conventional SR based DFF. Thus total power dissipated in the proposed circuit gets reduced.

#### References

- [1]. [1] S. Natarajanet al., "A 14nm logic technology featuring 2nd-generation FinFET, air-gapped interconnects, self-aligned double patterning and a 0.0588 µm2 SRAM cell size," in Proc. IEEE Int. Electron DevicesMeeting, Dec. 2014, pp. 3 7. [2] M. Yabuuchiet al., "16 nm FinFET high-k/Metal-gate 256-kbit 6T SRAM macros with wordline overdriven assist," in Proc.

- [2]. IEEE Int.Electron Devices Meeting, Dec. 2014, pp. 3.3.1-3.3.3.

- [3] T. Mizuno, J. -I. Okamura, and A. Toriumi, "Experimental study of threshold voltage fluctuation due to statistical variation of [3]. channel dopant number in MOSFET's," IEEE Trans. Electron Devices, vol. 41, no. 11, pp. 2216–2221, Nov. 1994.

- [4]CH. Ashok Babu, J.V.R. Ravindra and K. Lal Kishore "Novel Circuit Level Leakage Power Reduction Technique for Ultra Low [4]. Power and high speed VLSI circuits," International Journal of Communication Engineering Applications, vol. 3, Aug-Dec 2012, pp. 508-514.

- [5]D. Kumar Gautam, Dr. S.R.P. Sinha and Er. Y. Kumar Verma, "Design a Low Power Half Subtractor Using AVL Technique [5]. Based on 65nm CMOS Technology," International Journal of Advanced Research in Computer Engineering and Technology, vol. 2, Nov. 2013, pp. 2891-2897.

- [6]A. Rjoub, and A. Shatnawi, "High Speed Low Power Multi threshold Voltage Flip Flops," Journal of Electrical Engineering, vol. [6]. 54, 2003, pp. 123-127.